**High-performance Regulator IC Series for PCs**

# **Ultra Low Dropout Linear Regulators for PC**

**BD3550HFN, BD3551HFN, BD3552HFN**

$(0.5 \sim 2.0 A)$

# Description

BD3550HFN,BD3551HFN,BD3552HFN ultra low-dropout linear chipset regulator operates from a very low input supply, and offers ideal performance in low input voltage to low output voltage applications. It incorporates a built-in N-MOSFET power transistor to minimize the input-to-output voltage differential to the ON resistance (Ron= $100 \text{m}\Omega$  <BD3552HFN>) level. By lowering the dropout voltage in this way, the regulator realizes high current output (Iomax=2.0A <BD3552HFN>) with reduced conversion loss, and thereby obviates the switching regulator and its power transistor, choke coil, and rectifier diode. Thus, BD3550HFN,BD3551HFN,BD3552HFN is designed to enable significant package profile downsizing and cost reduction. An external resistor allows the entire range of output voltage configurations between 0.65 and 2.7V, while the NRCS (soft start) function enables a controlled output voltage ramp-up, which can be programmed to whatever power supply sequence is required.

# Features

- 1) Internal high-precision reference voltage circuit(0.65V±1%)

- 2) Built-in VCC undervoltage lockout circuit

- 3) NRCS (soft start) function reduces the magnitude of in-rush current

- 4) Internal Nch MOSFET driver offers low ON resistance (100m Ω <BD3552HFN typ>)

- 5) Built-in current limit circuit

- 6) Built-in thermal shutdown (TSD) circuit

- 7) Variable output (0.65~2.7V)

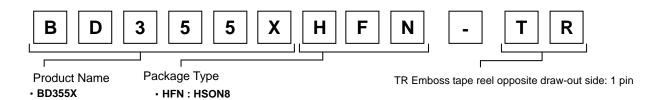

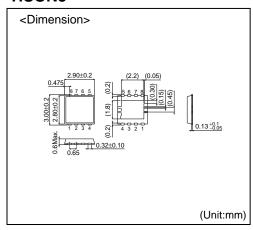

- 8) Small package HSON8: 2.9 × 3 × 0.6(mm)

- 9) Tracking function

### **Applications**

Notebook computers, Desktop computers, LCD-TV, DVD, Digital appliances

# Line-up

It is available to select power supply voltage and maximum output voltage.

| Maximum Output Voltage | Package | Vcc=5V    |

|------------------------|---------|-----------|

| 0.5A                   |         | BD3550HFN |

| 1.0A                   | HSON8   | BD3551HFN |

| 2.0A                   |         | BD3552HFN |

Oct. 2008

# Absolute maximum ratings

# **©BD3550HFN,BD3551HFN,BD3552HFN**

| Danamatan                    | 0      | Limit               |                     |           | 1.124 |

|------------------------------|--------|---------------------|---------------------|-----------|-------|

| Parameter                    | Symbol | BD3550HFN           | BD3551HFN           | BD3552HFN | Unit  |

| Input Voltage 1              | VCC    |                     | +6.0 *1             |           |       |

| Input Voltage 2              | VIN    |                     | +6.0 * <sup>1</sup> |           | V     |

| Enable Input Voltage         | Ven    | -0.3~+6.0           |                     |           | V     |

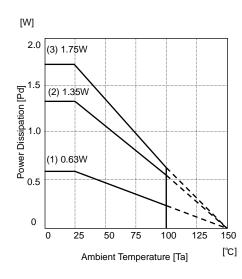

| Power Dissipation 1          | Pd1    | 0.63 *2             |                     |           | W     |

| Power Dissipation 2          | Pd2    | 1.35 * <sup>3</sup> |                     |           | W     |

| Power Dissipation 3          | Pd3    | 1.75 * <sup>4</sup> |                     |           | W     |

| Operating Temperature Range  | Topr   | -10 <b>~</b> +100   |                     | °C        |       |

| Storage Temperature Range    | Tstg   | -55 <b>∼</b> +150   |                     | °C        |       |

| Maximum Junction Temperature | Tjmax  | +150                |                     |           | °C    |

<sup>\*1</sup> Should not exceed Pd.

<sup>\*2</sup> Reduced by 5.04mW/°C for each increase in Ta≥25°C (when mounted on a 70mm×70mm×1.6mm glass-epoxy board, 1-layer)

On less than 0.2% (percentage occupied by copper foil.

\*3 Reduced by 10.8mW/°C for each increase in Ta≥25°C (when mounted on a 70mm×70mm×1.6mm glass-epoxy board, 1-layer)

On less than 7.0% (percentage occupied by copper foil.

<sup>\*4</sup> Reduced by 14.0mW/°C for each increase in Ta≥25°C (when mounted on a 70mm×70mm×1.6mm glass-epoxy board, 1-layer) On less than 65.0% (percentage occupied by copper foil.

# **©BD3550HFN,BD3551HFN,BD3552HFN**

# ● Operating Voltage(Ta=25°C)

| Parameter                    | Symbol | Min.  | Max.     | Unit |

|------------------------------|--------|-------|----------|------|

| Input Voltage 1              | VCC    | 4.3   | 5.5      | V    |

| Input Voltage 2              | VIN    | 0.95  | VCC-1 *5 | V    |

| Output Voltage Setting Range | Vo     | VFB   | 2.7      | V    |

| Enable Input Voltage         | Ven    | 0     | 5.5      | V    |

| NRCS Capacity                | CNRCS  | 0.001 | 1        | μF   |

<sup>\*5</sup> VCC and VIN do not have to be implemented in the order listed.

# ullet Electrical Characteristics (Unless otherwise specified, Ta=25°C, VCC=5V, Ven=3V, VIN=1.8V, R1=3.9K $\Omega$ , R2=3.3K $\Omega$ )

|                                          | ,         |                  | ,     | Limit | · · · |      | - 1.0 V, K1=0.0KE, K2=0.0KE)                  |

|------------------------------------------|-----------|------------------|-------|-------|-------|------|-----------------------------------------------|

| Paramete                                 | r         | Symbol           | Min.  | Тур.  | Max.  | Unit | Condition                                     |

| Bias Current                             |           | ICC              | -     | 0.5   | 1.0   | mA   |                                               |

| VCC Shutdown Mode                        | e Current | IST              | -     | 0     | 10    | uA   | Ven=0V                                        |

| Output Voltage                           |           | VOUT             | -     | 1.200 | -     | V    |                                               |

| Output Voltage Temp<br>Coefficient       | erature   | Tcvo             | -     | 0.01  | -     | %/°C |                                               |

| Feedback Voltage 1                       |           | VFB1             | 0.643 | 0.650 | 0.657 | V    |                                               |

| Feedback Voltage 2                       |           | VFB2             | 0.637 | 0.650 | 0.663 | V    | Tj=-10 to 100°C                               |

| Load Regulation                          |           | Reg.L            | -     | 0.5   | 10    | mV   | lo=0 to 1A<br>(BD3550HFN lo=0A to 0.5A)       |

| Line Regulation 1                        |           | Reg.l1           | -     | 0.1   | 0.5   | %/V  | VCC=4.3V to 5.5V                              |

| Line Regulation 2                        |           | Reg.l2           | -     | 0.1   | 0.5   | %/V  | VIN=1.2V to 3.3V                              |

| Standby Discharge C                      | Current   | Iden             | 1     | -     | -     | mA   | Ven=0V, Vo=1V                                 |

| [ENABLE]                                 |           |                  |       |       |       |      |                                               |

| Enable Pin<br>Input Voltage High         |           | Enhi             | 2     | -     | -     | V    |                                               |

| Enable Pin Input Voltage Low             |           | Enlow            | 0     | -     | 0.8   | V    |                                               |

| Enable Input Bias Cu                     | ırrent    | len              | -     | 7     | 10    | μΑ   | Ven=3V                                        |

| [FEEDBACK]                               |           | _                |       |       |       | 1    |                                               |

| Feedback Pin Bias C                      | urrent    | IFB              | -100  | 0     | 100   | nA   |                                               |

| [NRCS]                                   |           | 1                |       |       |       | I.   | 1                                             |

| NRCS Charge Curre                        | nt        | Inrcs            | 14    | 20    | 26    | μΑ   | Vnrcs=0.5V                                    |

| NRCS Standby Volta                       |           | VSTB             | -     | 0     | 50    | mV   | Ven=0V                                        |

| [UVLO]                                   |           |                  |       |       |       | •    |                                               |

| VCC Undervoltage L<br>Threshold Voltage  | ockout    | VccUVLO          | 3.5   | 3.8   | 4.1   | V    | Vcc:Sweep-up                                  |

| VCC Undervoltage L<br>Hysteresis Voltage | ockout    | Vcchys           | 100   | 160   | 220   | mV   | Vcc:Sweep-down                                |

| [AMP]                                    |           |                  |       |       |       |      |                                               |

| Gate Source Current                      |           | I <sub>GSO</sub> | -     | 1.6   | -     | mA   | V <sub>FB</sub> =0, V <sub>GATE</sub> =2.5V   |

| Gate Sink Current                        | _         | I <sub>GSI</sub> | -     | 4.7   | -     | mA   | V <sub>FB</sub> =VCC, V <sub>GATE</sub> =2.5V |

| Maximum output                           | BD3550HFN | lo               | 0.5   | -     | -     | Α    |                                               |

| current                                  | BD3551HFN | lo               | 1.0   | -     | -     | Α    |                                               |

| Odifont                                  | BD3552HFN | lo               | 2.0   | -     | -     | Α    |                                               |

| Minimum dropout                          | BD3550HFN | dVo              | -     | 200   | 300   | mV   | Io=0.5A, VIN=1.2V, Ta=-10 to 100°C            |

| voltage                                  | BD3551HFN | dvo              | -     | 200   | 300   | mV   | Io=1.0A, VIN=1.2V, Ta=-10 to 100°C            |

|                                          | BD3552HFN | dVo              | -     | 200   | 300   | mV   | Io=2.0A, VIN=1.2V, Ta=-10 to 100°C            |

<sup>★</sup>This product is not designed for use in radioactive environments.

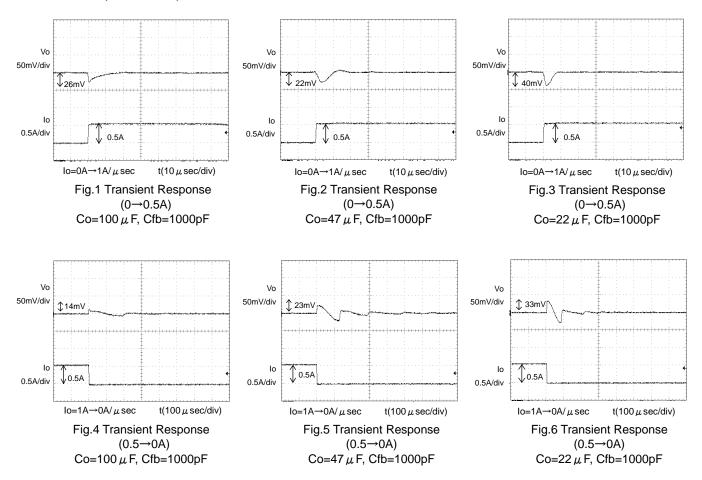

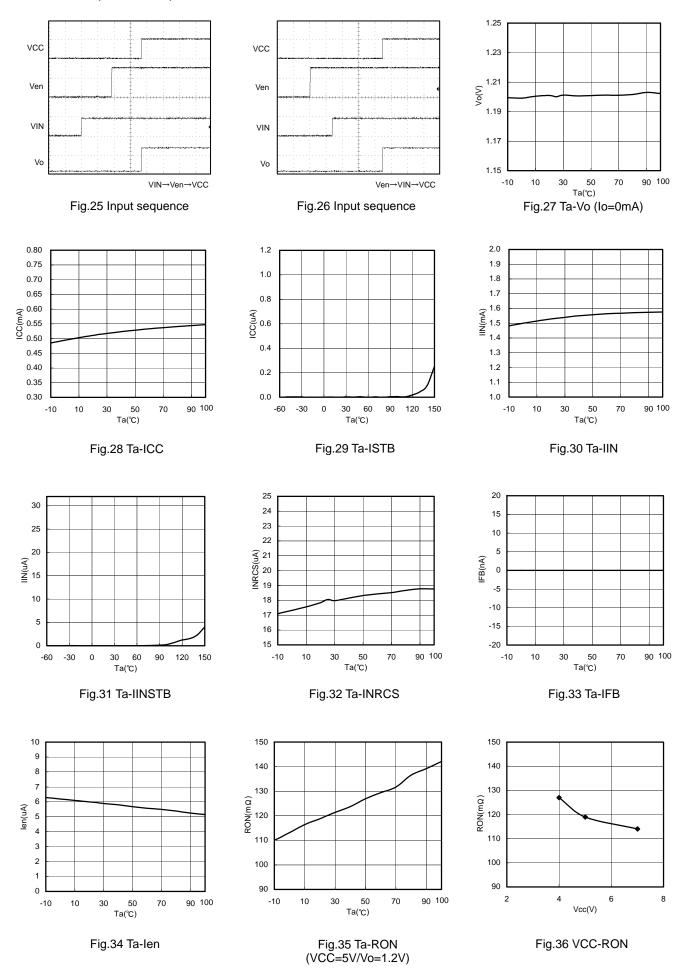

# ● Reference Data(BD3550HFN)

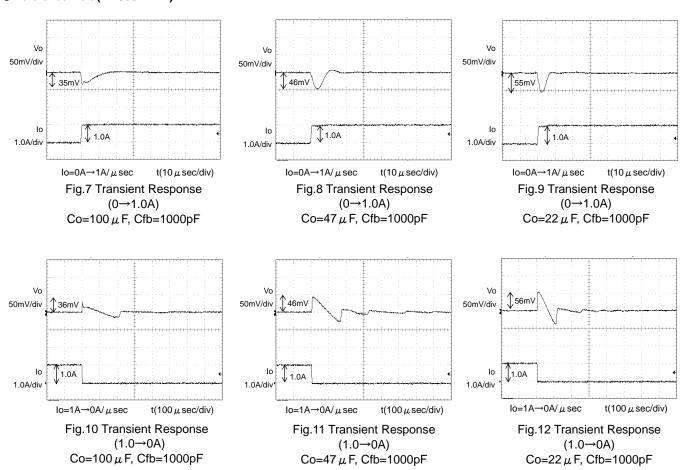

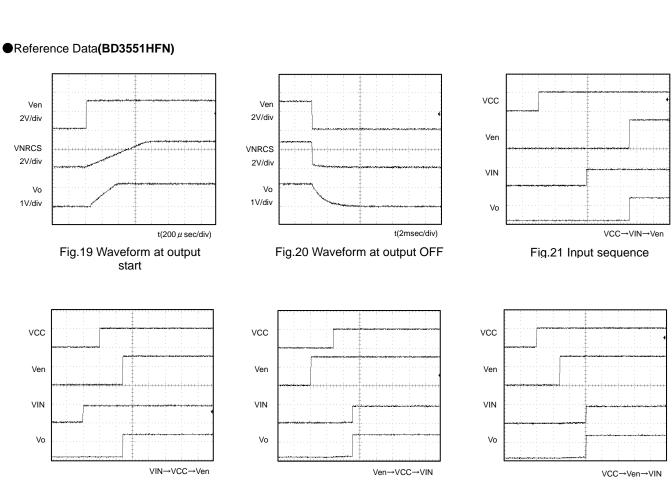

# ● Reference Data(BD3551HFN)

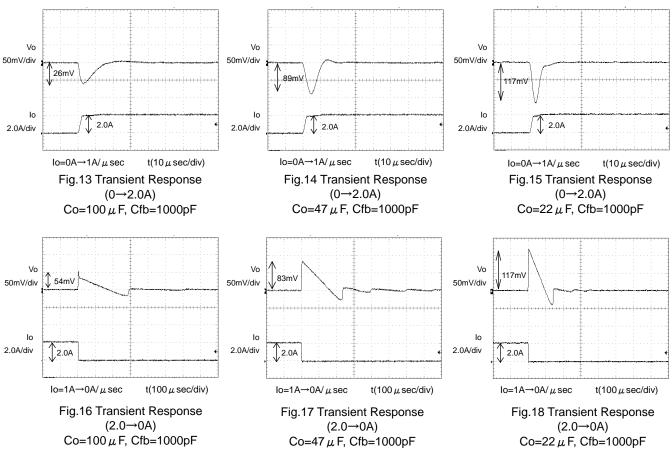

# ● Reference Data(BD3552HFN)

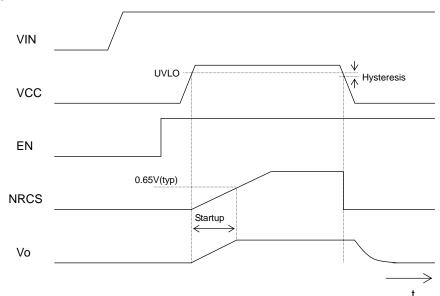

Fig.22 Input sequence

Fig.24 Input sequence

Fig.23 Input sequence

# ● Reference Data(BD3551HFN)

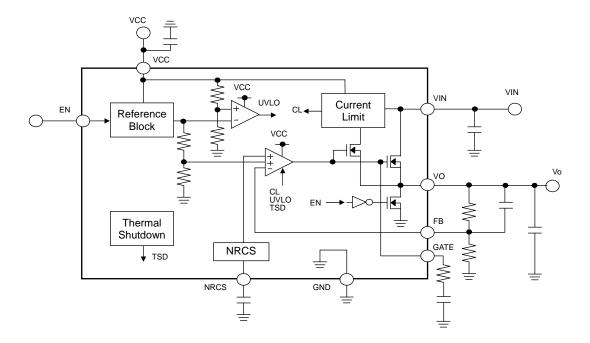

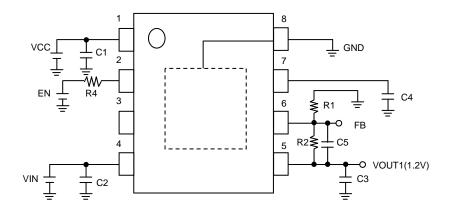

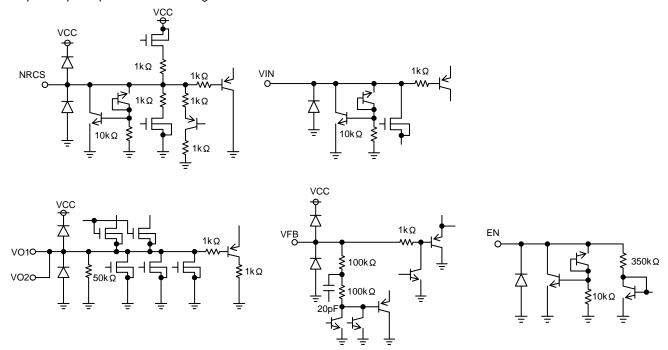

# ●Block Diagram

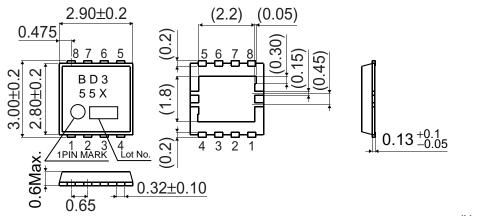

# ●Pin Layout

| PIN No. | PIN name | PIN Function                                               |

|---------|----------|------------------------------------------------------------|

| 1       | VCC      | Power supply pin                                           |

| 2       | EN       | Enable input pin                                           |

| 3       | GATE     | Gate pin                                                   |

| 4       | VIN      | Input voltage pin                                          |

| 5       | VO       | Output voltage pin                                         |

| 6       | FB       | Reference voltage feedback pin                             |

| 7       | NRCS     | In-rush current protection (NRCS) capacitor connection pin |

| 8       | GND      | Ground pin                                                 |

| reverse | FIN      | Connected to heatsink and GND                              |

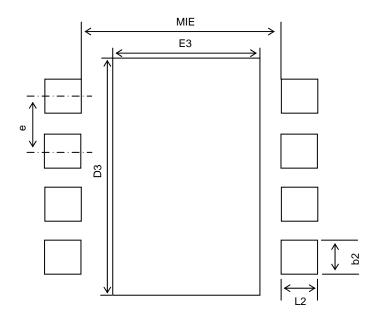

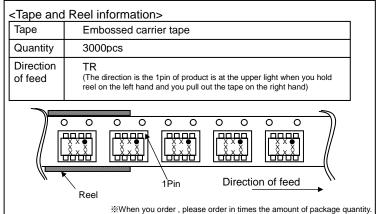

# ●Pin Function Table ◎HSON8

(Unit: mm)

#### Operation of Each Block

#### AMP

This is an error amp that compares the reference voltage (0.65V) with Vo to drive the output Nch FET (Ron=100m  $\Omega$ :BD3552HFN). Frequency optimization helps to realize rapid transient response, and to support the use of ceramic capacitors on the output. AMP input voltage ranges from GND to 2.7V, while the AMP output ranges from GND to VCC. When EN is OFF, or when UVLO is active, output goes LOW and the output of the NchFET switches OFF.

#### • EN

The EN block controls the regulator's ON/OFF state via the EN logic input pin. In the OFF position, circuit voltage is maintained at  $0 \mu$  A, thus minimizing current consumption at standby. The FET is switched ON to enable discharge of the NRCS pin Vo, thereby draining the excess charge and preventing the IC on the load side from malfunctioning. Since no electrical connection is required (e.g., between the VCC pin and the ESD prevention Diode), module operation is independent of the input sequence.

#### UVLO

To prevent malfunctions that can occur during a momentary decrease in VCC, the UVLO circuit switches the output OFF, and (like the EN block) discharges NRCS and Vo. Once the UVLO threshold voltage (TYP3.80V) is reached, the power-on reset is triggered and output continues.

#### CURRENT LIMIT

When output is ON, the current limit function monitors the internal IC output current against the parameter value (2.0A or more:BD3552HFN). When current exceeds this level, the current limit module lowers the output current to protect the load IC. When the overcurrent state is eliminated, output voltage is restored to the parameter value.

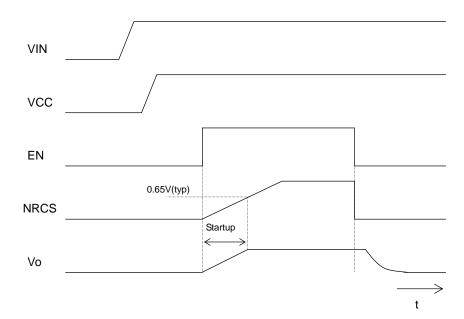

# · NRCS (Non Rush Current on Start-up)

The soft start function enabled by connecting an external capacitor between the NRCS pin and ground. Output ramp-up can be set for any period up to the time the NRCS pin reaches VFB (0.65V). During startup, the NRCS pin serves as a 20  $\mu$  A (TYP) constant current source to charge the external capacitor. Output start time is calculated via formula (1) below.

$$t = C \frac{0.65V}{20 \,\mu A} \cdot \cdot \cdot (1)$$

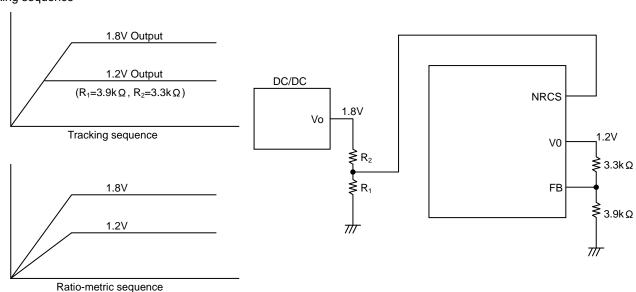

Tracking sequence is available by connecting the output voltage of external power supply instead of external capacitor. And then, ratio-metric sequence is also available by changing the resistor division ratio of external power supply output voltage. (See the next page)

# TSD (Thermal Shut down)

The shutdown (TSD) circuit automatically switches output OFF when the chip temperature gets too high, thus serving to protect the IC against "thermal runaway" and heat damage. Because the TSD circuit is provided to shut down the IC in the presence of extreme heat, in order to avoid potential problems with the TSD, it is crucial that the Tj (max) parameter not be exceeded in the thermal design.

#### VIN

The VIN line acts as the major current supply line, and is connected to the output NchFET drain. Since no electrical connection (such as between the VCC pin and the ESD protection Diode) is necessary, VIN operates independent of the input sequence. However, since an output NchFET body Diode exists between VIN and Vo, a VIN-Vo electric (Diode) connection is present. Note, therefore, that when output is switched ON or OFF, reverse current may flow to VIN from Vo.

# ●Timing Chart EN ON/OFF

# VCC ON/OFF

# Tracking sequence

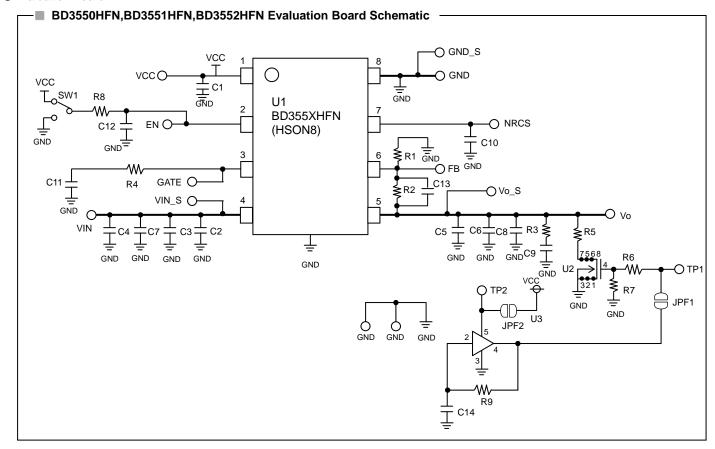

# Evaluation Board

# ■ BD3550HFN,BD3551HFN,BD3552HFN Evaluation Board Standard Component List

| Component | Rating | Manufacturer | Product Name    |

|-----------|--------|--------------|-----------------|

| U1        | -      | ROHM         | BD355XHFN       |

| C1        | 1uF    | MURATA       | GRM188B11A105KD |

| C10       | 0.01uF | MURATA       | GRM188B11H103KD |

| R8        | 0Ω     | -            | Jumper          |

| C5        | 22uF   | KYOCERA      | CM32X5R226M10A  |

| Component | Rating | Manufacturer | Product Name    |

|-----------|--------|--------------|-----------------|

| C2        | 22uF   | KYOCERA      | CM32X5R226M10A  |

| C13       | 1000pF | MURATA       | GRM188B11H102KD |

| R1        | 3.9kΩ  | ROHM         | MCR03EZPF3301   |

| R2        | 3.3kΩ  | ROHM         | MCR03EZPF3901   |

|           |        |              |                 |

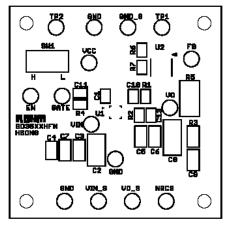

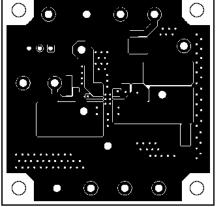

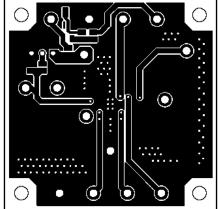

# ■ BD3550HFN,BD3551HFN,BD3552HFN Evaluation Board Layout

(2nd layer and 3rd layer is GND Line.)

Silkscreen TOP Layer Bottom Layer

| Component | Recommended Value           | Programming Notes and Precautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1/R2     | 3.9k/3.3k                   | IC output voltage can be set with a configuration formula using the values for the internal reference output voltage ( $V_{FB}$ )and the output voltage resistors (R1, R2). Select resistance values that will avoid the impact of the VREF current ( $\pm 100$ nA). The recommended total resistance value is $10$ K $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C3        | 22 μ F                      | To assure output voltage stability, please be certain the Vo1, Vo2, and Vo3 pins and the GND pins are connected. Output capacitors play a role in loop gain phase compensation and in mitigating output fluctuation during rapid changes in load level. Insufficient capacitance may cause oscillation, while high equivalent series reisistance (ESR) will exacerbate output voltage fluctuation under rapid load change conditions. While a $22\mu$ F ceramic capacitor is recomended, actual stability is highly dependent on temperature and load conditions. Also, note that connecting different types of capacitors in series may result in insufficient total phase compensation, thus causing oscillation. In light of this information, please confirm operation across a variety of temperature and load conditions. |

| C1        | 1 μ F                       | Input capacitors reduce the output impedance of the voltage supply source connected to the (VCC) input pins. If the impedance of this power supply were to increase, input voltage (VCC) could become unstable, leading to oscillation or lowered ripple rejection function. While a low-ESR 1 $\mu$ F capacitor with minimal susceptibility to temperature is recommended, stability is highly dependent on the input power supply characteristics and the substrate wiring pattern. In light of this information, please confirm operation across a variety of temperature and load conditions.                                                                                                                                                                                                                               |

| C2        | 22 μ F                      | Input capacitors reduce the output impedance of the voltage supply source connected to the (VIN) input pins. If the impedance of this power supply were to increase, input voltage (VIN) could become unstable, leading to oscillation or lowered ripple rejection function. While a low-ESR 22 $\mu$ F capacitor with minimal susceptibility to temperature is recommended, stability is highly dependent on the input power supply characteristics and the substrate wiring pattern. In light of this information, please confirm operation across a variety of temperature and load conditions.                                                                                                                                                                                                                              |

| C4        | 0.01 μ F                    | The Non Rush Current on Startup (NRCS) function is built into the IC to prevent rush current from going through the load (VIN to VO) and impacting output capacitors at power supply start-up. Constant current comes from the NRCS pin when EN is HIGH or the UVLO function is deactivated. The temporary reference voltage is proportionate to time, due to the current charge of the NRCS pin capacitor, and output voltage start-up is proportionate to this reference voltage. Capacitors with low susceptibility to temperature are recommended, in order to assure a stable soft-start time.                                                                                                                                                                                                                             |

| C5        | -                           | This component is employed when the C3 capacitor causes, or may cause, oscillation. It provides more precise internal phase correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| R4        | Several kΩ<br>∼several 10kΩ | It is recommended that a resistance (several $k\Omega$ to several $10k\Omega$ ) be put in R4, in case negative voltage is applied in EN pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Heat Loss

Thermal design should allow operation within the following conditions. Note that the temperatures listed are the allowed temperature limits, and thermal design should allow sufficient margin from the limits.

- 1. Ambient temperature Ta can be no higher than 100°C.

- 2. Chip junction temperature (Tj) can be no higher than 150°C.

Chip junction temperature can be determined as follows:

① Calculation based on ambient temperature (Ta) Tj=Ta+ θ j-a×W

<Reference values>

$\theta$  j-a:HSON8 198.4°C/W 1-layer substrate (copper foil density 0.2%) 92.4°C/W 1-layer substrate (copper foil density 7%) 71.4°C/W 2-layer substrate (copper foil density 65%) Substrate size:  $70 \times 70 \times 1.6$ mm³ (substrate with thermal via)

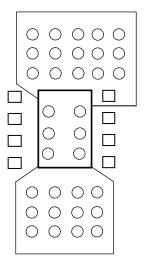

It is recommended to layout the VIA for heat radiation in the GND pattern of reverse (of IC) when there is the GND pattern in the inner layer (in using multiplayer substrate). This package is so small (size:  $2.9 \text{mm} \times 3.0 \text{mm}$ ) that it is not available to layout the VIA in the bottom of IC. Spreading the pattern and being increased the number of VIA like the figure below). enable to get the superior heat radiation characteristic. (This figure is the image. It is recommended that the VIA size and the number is designed suitable for the actual situation.).

Most of the heat loss that occurs in BD3550HFN,BD3551HFN,BD3552HFN is generated from the output Nch FET. Power loss is determined by the total VIN-Vo voltage and output current. Be sure to confirm the system input and output voltage and the output current conditions in relation to the heat dissipation characteristics of the VIN and Vo in the design. Bearing in mind that heat dissipation may vary substantially depending on the substrate employed (due to the power package incorporated in BD3550HFN,BD3551HFN,BD3552HFN) make certain to factor conditions such as substrate size into the thermal design.

Power consumption (W) =

$$\left\{ \text{Input voltage (VIN)- Output voltage (Vo) (Vo $\rightleftharpoons$ VREF)} \right\} \times \text{Io(Ave)}$$

Example) Where VIN=1.8V, VO=1.2V, Io(Ave) = 1A,

Power consumption (W) =  $\left\{ 1.8(\text{V})-1.2(\text{V}) \right\} \times 1.0(\text{A})$

= 0.6(W)

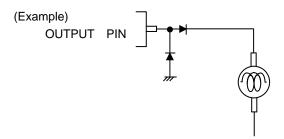

# ●Input-Output Equivalent Circuit Diagram

# ■Reference landing pattern

(Unit:mm)

| Lead pitch         | Lead pitch        | landing length | landing pitch |

|--------------------|-------------------|----------------|---------------|

|                    |                   | >              |               |

| е                  | MIE               | ≧12            | b2            |

| 0.65               | 2.50              | 0.40           | 0.35          |

| central pad length | central pad pitch |                |               |

|                    |                   |                |               |

| D3                 | E3                |                |               |

| 2.90               | 1.90              |                |               |

<sup>\*</sup>It is recommended to design suitable for the actual application.

#### Operation Notes

#### 1. Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as fuses.

# 2. Connecting the power supply connector backward

Connecting of the power supply in reverse polarity can damage IC. Take precautions when connecting the power supply lines. An external direction diode can be added.

#### 3. Power supply lines

Please add a protection diode when a large inductance component is connected to the output terminal, and reverse-polarity power is possible at startup or in output OFF condition.

#### 4. GND voltage

The potential of GND pin must be minimum potential in all operating conditions.

#### 5. Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

# 6. Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any connection error or if pins are shorted together.

### 7. Actions in strong electromagnetic field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to malfunction.

# 8. ASO

When using the IC, set the output transistor so that it does not exceed absolute maximum ratings or ASO.

## 9. Thermal shutdown circuit

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed only to shut the IC off to prevent thermal runaway. It is not designed to protect the IC or guarantee its operation. Do not continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is assumed.

|                               | TSD on temperature [°C] | Hysteresis temperature [°C] |

|-------------------------------|-------------------------|-----------------------------|

|                               | (typ.)                  | (typ.)                      |

| BD3550HFN,BD3551HFN,BD3552HFN | 175                     | 15                          |

## 10. Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress. Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to or removing it from a jig or fixture during the inspection process. Ground the IC during assembly steps as an antistatic measure. Use similar precaution when transporting or storing the IC.

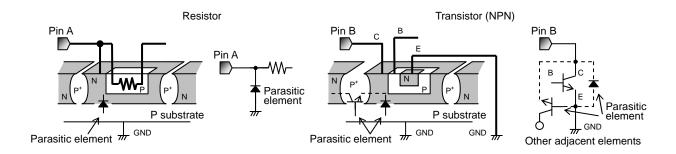

# 11. Regarding input pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or transistor. For example, the relation between each potential is as follows:

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes can occur inevitable in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

# 12. Ground Wiring Pattern.

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns, placing a single ground point at the ground potential of application so that the pattern wiring resistance and voltage variations caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the GND wiring pattern of any external components, either.

# Heat Dissipation Characteristics

# **©HSON8**

- (1) Substrate (copper foil density: 0.2%...1-layer)  $\theta$  j-a=198.4°C/W

- (2) Substrate (copper foil density: 7%...1-layer)  $\theta$  j-a=92.4°C/W

- (3) Substrate (copper foil density: 65%...1-layer)  $\theta$  j-a=71.4°C/W

# **HSON8**

- The contents described herein are subject to change without notice. For updates of the latest information, please contact and confirm with ROHM CO.,LTD.

- Any part of this application note must not be duplicated or copied without our permission.

Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding

- Any data, including, but not limited to application circuit diagrams and information, described herein, are intended only as illustrations of such devices and not as the specifications for such devices, BOHM, CO., LTD, disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD, is granted to any such buyer.

- The products described herein utilize silicon as the main material.

The products described herein are not designed to be X ray proof.

The products listed in this catalog are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

Excellence in Electronics

ROHM CO., LTD.

21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

URL http://www.rohm.com

Published by KTC LSI Development Headquarters LSI Business Pomotion Group

Contact us for further information about the products. San Diego Atlanta Boston Chicago Denver Detroit Nashville Düsseldorf Stuttgart France United Kinadon Oulu Barcelona Hungary Poland Russia Seoul Masan Beijing

TEL: +1-858-625-3630 FAX: +1-858-625-3670 FAX: +1-858-625-3670 FAX: +1-770-754-0691 FAX: +1-928-438-7164 FAX: +1-847-368-1008 FAX: +1-469-362-7973 FAX: +1-303-708-0858 TEL: +1-770-754-5972 TEL: +1-978-371-0382 TEL: +1-978-371-0382 TEL: +1-847-368-1006 TEL: +1-469-287-5366 TEL: +1-303-708-0908 TEL: +1-248-348-9920 FAX: +1-248-348-9942 FAX: +1-615-620-6702 TEL: +1-615-620-6700 TEL: +1-013-020-0700 TEL: +52-33-3123-2001 TEL: +49-2154-9210 TEL: +49-8999-216168 TEL: +49-711-7272-370 FAX: +15-13-320-07-02 FAX: +52-33-3123-2002 FAX: +49-2154-921400 FAX: +49-8999-216176 FAX: +49-711-7272-3720 TEL: +33-1-5697-3060 FAX: +33-1-5697-3080 TEL: +44-1-908-306700 FAX: +44-1-908-235788 TEL: +44-1-908-30700 TEL: +45-3694-4739 TEL: +358-9725-54491 TEL: +358-2-7332234 TEL: +358-8-5372930 FAX: +45-3694-4789 FAX: +45-3694-4769 FAX: +358-9-7255-4499 FAX: +358-2-7332237 FAX: +358-8-5372931 FAX: +34-9375-24410 TEL: +34-9375-24320 TEL: +36-1-4719338 FAX: +36-1-4719339 TEL: +48-22-5757213 FAX: +48-22-5757001 TEL: +7-495-739-41-74 FAX: +7-495-739-41-74 TEL: +82-8-182-700 FAX: +82-9-8182-715

TEL: +82-55-240-6234 FAX: +82-55-240-6236

TEL: +86-411-8230-8537

TEL: +86-10-8525-2483 FAX: +86-10-8525-2489

Shanghai Hangzhou Nanjing Ningbo Qingdao Suzhou Wuxi Shenzher Dongguan Guangzhou Huizhou Zhuha Hong Kong Taipei Kaohsiung Singapore Philippines Thailand Kuala Lumpu

Tianjin

TEL: +86-22-23029181 FAX: +86-22-23029183 FAX: +86-22-23029183 FAX: +86-21-6247-2066 FAX: +86-571-87658071 FAX: +86-25-8689-0393 FAX: +86-574-87654208 FAX:+86-532-5779-653 TEL: +86-21-6279-2727 TEL: +86-21-6279-2727 TEL: +86-571-87658072 TEL: +86-25-8689-0015 TEL: +86-574-87654201 TEL: +86-532-5779-312 TEL: +86-512-6807-1300 FAX: +86-512-6807-2300 TEL: +86-510-82702693 FAX: +86-510-82702992 TEL: +86-510-92702693 FAX: +86-510-92702992 FEL: +86-75-8307-3003 TEL: +86-769-8393-3320 FAX: +86-769-8398-4140 TEL: +86-591-8801-8698 FAX: +86-753-825-9695 TEL: +86-752-205-1054 FAX: +86-752-205-1059 TEL: +86-752-205-1054

TEL: +86-756-3232-480

TEL: +86-756-3232-480

TEL: +886-2-2500-6956

TEL: +886-7-237-0881

TEL: +65-6332-2322 FAX: +86-592-239-8380 FAX: +86-756-3232-460 FAX: +86-7-30-3232-4400 FAX: +852-2-375-8971 FAX: +886-2-2503-2869 FAX: +886-7-238-7332 FAX: +65-6332-5662 TEL: +63-2-807-6872 FAX: +63-2-809-1422 FAX: +66-2-256-6334 TEL: +66-2-254-4890 TEL: +60-2-234-4690 TEL: +60-3-7958-8355 TEL: +60-4-2286453 TEL: +81-75-365-1218 TEL: +81-45-476-2290 FAX: +60-2-2-36-6334 FAX: +60-3-7958-8377 FAX: +60-4-2286452 FAX: +81-75-365-1228 FAX: +81-45-476-2295

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM CO..LTD.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact your nearest sales office.

**ROHM** Customer Support System

THE AMERICAS / EUROPE / ASIA / JAPAN

www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2008 ROHM CO.,LTD.

ROHM CO., LTD. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

an TEL:+81-75-311-2121 FAX:+81-75-315-0172