# CLC425 Ultra Low Noise Wideband Op Amp

## **General Description**

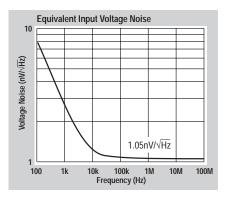

The CLC425 combines a wide bandwidth (**1.9GHz GBW**) with very low input noise (**1.05nV**/ $\sqrt{Hz}$ , **1.6pA**/ $\sqrt{Hz}$ ) and low dc errors (**100µV** V<sub>os</sub>, **2µV**/°C drift) to provide a very precise, wide dynamic-range op amp offering closed-loop gains of  $\geq$ 10.

Singularly suited for very wideband high-gain operation, the CLC425 employs a traditional voltage-feedback topology providing all the benefits of balanced inputs, such as low offsets and drifts, as well as a 96dB open-loop gain, a 100dB CMRR and a 95dB PSRR.

The CLC425 also offers great flexibility with its externally adjustable supply current, allowing designers to easily choose the optimum set of power, bandwidth, noise and distortion performance. Operating from  $\pm 5V$  power supplies, the CLC425 defaults to a 15mA quiescent current, or by adding one external resistor, the supply current can be adjusted to less than 5mA.

The CLC425's combination of ultra-low noise, wide gain-bandwidth, high slew rate and low dc errors will enable applications in areas such as medical diagnostic ultrasound, magnetic tape & disk storage, communications and opto-electronics to achieve maximum high-frequency signal-to-noise ratios.

The CLC425 is available in the following versions:

| CLC425AJP    | -40°C to +85°C     | 8-pin PDIP                 |

|--------------|--------------------|----------------------------|

| CLC425AJE    | -40°C to +85°C     | 8-pin SOIC                 |

| CLC425A8B    | -55°C to +125°C    | 8-pin CERDIP,              |

|              |                    | MIL-STD-883, Level B       |

| CLC425ALC    | -40°C to +85°C     | dice                       |

| CLC425AMC    | -55°C to +125°C    | dice, MIL-STD-883, Level B |

| CLC425AJM5   | -40°C to +85°C     | 5-pin SOT                  |

| DESC SMD nur | nber : 5962-93259. |                            |

## Features

- 1.9GHz gain-bandwidth product

- 1.05nV/√Hz input voltage noise

- 0.8pA/√Hz @ lcc ≤ 5mA

- 100µV input offset voltage, 2µV/°C drift

- 350V/µs slew rate

- 15mA to 5mA adjustable supply current

- Gain range ±10 to ±1,000V/V

- Evaluation boards & simulation macromodel

- 0.9dB NF @ R<sub>s</sub> = 700Ω

### **Applications**

- Instrumentation sense amplifiers

- Ultrasound pre-amps

- Magnetic tape & disk pre-amps

- Photo-diode transimpedance amplifiers

- Wide band active filters

- Low noise figure RF amplifiers

- Professional audio systems

- Low-noise loop filters for PLLs

| PARAMETERS                                    | CONDITIONS               | TYP   | MIN/MAX RATINGS |       |        | UNITS  | SYMBOL |

|-----------------------------------------------|--------------------------|-------|-----------------|-------|--------|--------|--------|

| Ambient Temperature                           | CLC425 AJ                | +25°C | -40°C           | +25°C | +85°C  |        |        |

| FREQUENCY DOMAIN RESPO                        | NSF                      |       |                 |       |        |        |        |

| gain bandwidth product                        | $V_{out} < 0.4 V_{pp}$   | 1.9   | 1.5             | 1.5   | 1.0    | GHz    | GBW    |

| -3dB bandwidth                                | $V_{out} < 0.4V_{pp}$    | 95    | 75              | 75    | 50     | MHz    | SSBW   |

|                                               | $V_{out} < 5.0V_{pp}$    | 40    | 30              | 30    | 20     | MHz    | LSBW   |

| gain flatness                                 | $V_{out} < 0.4 V_{pp}$   |       |                 |       |        |        |        |

| peaking                                       | DC to 30MHz              | 0.3   | 0.7             | 0.5   | 0.7    | dB     | GFP    |

| rolloff                                       | DC to 30MHz              | 0.1   | 0.7             | 0.5   | 0.7    | dB     | GFR    |

| linear phase deviation                        | DC to 30MHz              | 0.7   | 1.5             | 1.5   | 2.5    | 0      | LPD    |

| TIME DOMAIN RESPONSE                          |                          |       |                 |       |        |        |        |

| rise and fall time                            | 0.4V step                | 3.7   | 4.7             | 4.7   | 7.0    | ns     | TRS    |

| settling time to 0.2%                         | 2V step                  | 22    | 30              | 30    | 40     | ns     | TSS    |

| overshoot                                     | 0.4V step                | 5     | 12              | 10    | 12     | %      | OS     |

| slew rate                                     | 2V step                  | 350   | 250             | 250   | 200    | V/μs   | SR     |

| DISTORTION AND NOISE RESI                     |                          |       |                 |       |        |        |        |

| 2 <sup>nd</sup> harmonic distortion           | 1V <sub>pp</sub> , 10MHz | - 53  | 48              | 48    | 46     | dBc    | HD2    |

| 3 <sup>rd</sup> harmonic distortion           | 1V <sub>pp</sub> , 10MHz | - 75  | 65              | 65    | 60     | dBc    | HD3    |

| 3 <sup>rd</sup> order intermodulation interce | pt 10MHz                 | 35    |                 |       |        | dBm    | IMD    |

| equivalent noise input                        |                          |       |                 |       |        |        |        |

| voltage                                       | 1MHz to 100MHz           | 1.05  | 1.25            | 1.25  | 1.8    | nV/√Hz | VN     |

| current                                       | 1MHz to 100MHz           | 1.6   | 4.0             | 2.5   | 2.5    | pA/√Hz | ICN    |

| noise figure                                  | R <sub>s</sub> = 700Ω    | 0.9   |                 |       |        | dB     | NF     |

| STATIC DC PERFORMANCE                         |                          |       |                 |       |        |        |        |

| open-loop gain                                | DC                       | 96    | 77              | 86    | 86     | dB     | AOL    |

| *input offset voltage                         |                          | ± 100 | ± 1000          | ± 800 | ± 1000 | μV     | VIO    |

| average drift                                 |                          | ±2    | 8               |       | 4      | μV/°C  | DVIO   |

| *input bias current                           |                          | 12    | 40              | 20    | 20     | μΑ     | IB     |

| average drift                                 |                          | - 100 | - 250           |       | - 120  | nA/°C  | DIB    |

| input offset current                          |                          | ± 0.2 | 3.4             | 2.0   | 2.0    | μΑ     | lio    |

| average drift                                 |                          | ± 3   | ± 50            |       | ± 25   | nA/°C  | DIIO   |

| power supply rejection ratio                  | DC                       | 95    | 82              | 88    | 86     | dB     | PSRR   |

| common mode rejection ratio                   | DC                       | 100   | 88              | 92    | 90     | dB     | CMRR   |

| *supply current                               | R <sub>L</sub> = ∞       | 15    | 18              | 16    | 16     | mA     | ICC    |

| MISCELLANEOUS PERFORMA                        |                          |       |                 |       |        |        |        |

| input resistance                              | common-mode              | 2     | 0.6             | 1.6   | 1.6    | MΩ     | RINC   |

|                                               | differential-mode        | 6     |                 | 3     | 3      | kΩ     | RIND   |

| input capacitance                             | common-mode              | 1.5   | 2               | 2     | 2      | pF     | CINC   |

|                                               | differential-mode        | 1.9   | 3               | 3     | 3      | pF     | CIND   |

| output resistance                             | closed loop              | 5     | 50              | 10    | 10     | mΩ     | ROUT   |

| output voltage range                          | $R_{L} = \infty$         | ± 3.8 | ± 3.5           | ± 3.7 | ± 3.7  |        | VO     |

|                                               | $R_{L}=100\Omega$        | ± 3.4 | ± 2.8           | ± 3.2 | ± 3.2  |        | VOL    |

| input voltage range                           | common mode              | ± 3.8 | ± 3.4           | ± 3.5 | ± 3.5  | V      | CMIR   |

| output current                                | source                   | 80    | 70              | 70    | 70     | mA     | IOP    |

|                                               | sink                     | 80    | 45              | 55    | 55     | mA     | ION    |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

| V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                 | ±7V                                   | Recommended gain range ±10 to ±1,000V/V      |                  |                    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|------------------|--------------------|--|--|

| $      I_{out} \text{ short circuit protected to ground, however maximum reliability} \\ \text{ is obtained if } I_{out} \text{ does not exceed} 125 \text{mA} \\ \text{ common-mode input voltage } \pm V_{\text{oc}} \\ \text{ maximum junction temperature } +150^{\circ}\text{C} \\ \text{ operating temperature range: } $ |                                       | <b>Notes:</b><br>* AJ :100% tested at +25°C. |                  |                    |  |  |

|                                                                                                                                                                                                                                                                                                                                 |                                       | Package Thermal Resistance                   |                  |                    |  |  |

| AJ<br>storage temperature range                                                                                                                                                                                                                                                                                                 | -40°C to +85°C =<br>-65°C to +150°C _ | Package                                      | θ <sub>JC</sub>  | θ <sub>JA</sub>    |  |  |

| lead temperature (soldering 10 sec)                                                                                                                                                                                                                                                                                             | -03 C to +150 C _                     | AJP                                          | 70°C/W           | 125°C/W            |  |  |

| ESD (human body model)                                                                                                                                                                                                                                                                                                          | 1000V                                 | AJE<br>A8B                                   | 65°C/W<br>45°C/W | 145°C/W<br>135°C/W |  |  |

| Reliability Information                                                                                                                                                                                                                                                                                                         |                                       | AJM5                                         | 115°C/W          | 185°C/W            |  |  |

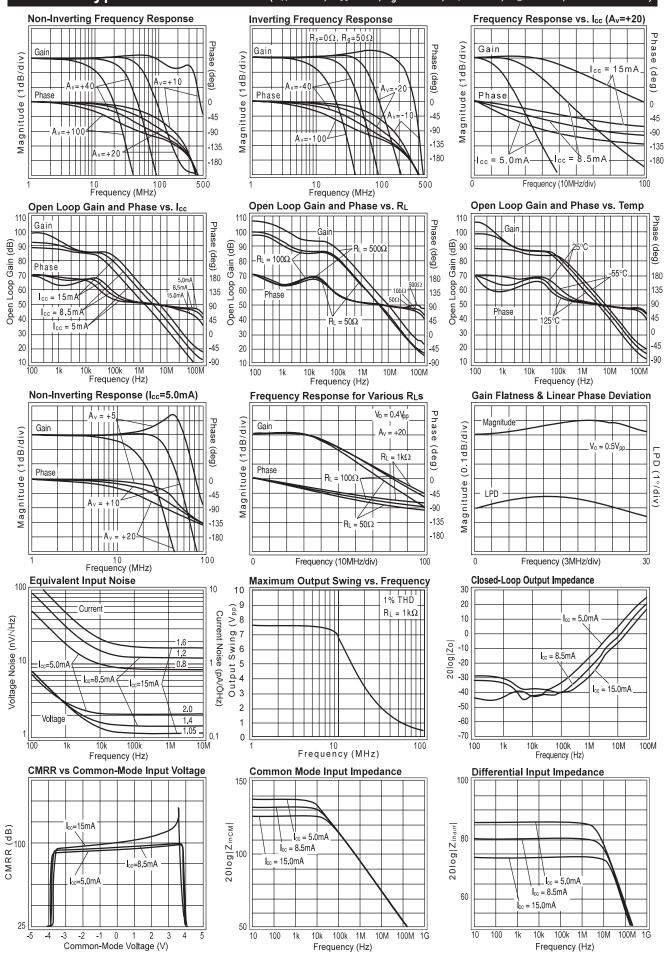

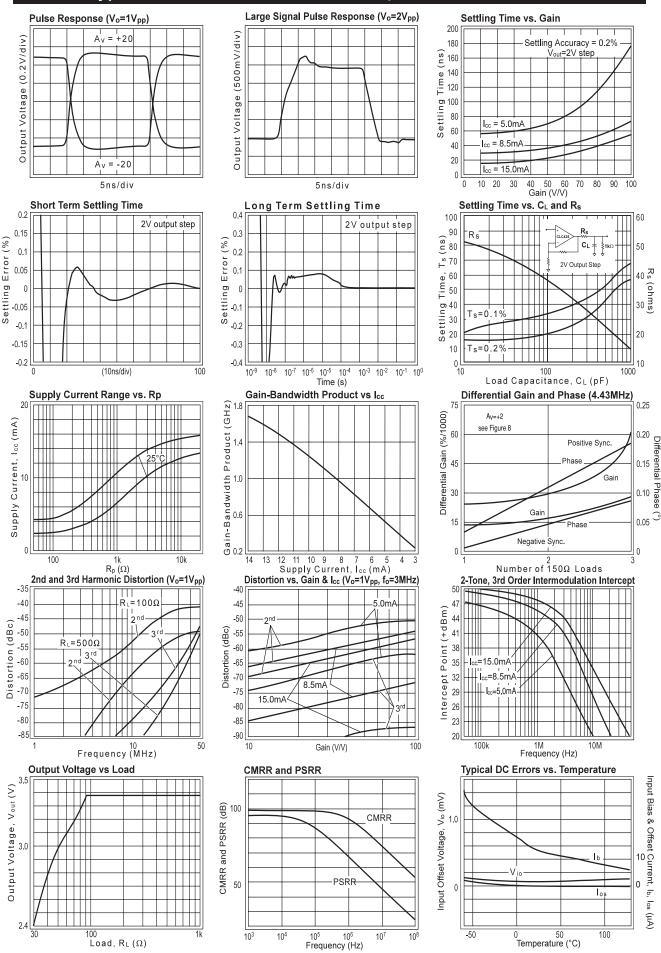

## CLC425 Typical Performance (T<sub>A</sub>=25°C, V<sub>cc</sub>= $\pm$ 5V,R<sub>g</sub>=26.1 $\Omega$ , R<sub>f</sub>=499 $\Omega$ , R<sub>L</sub>=100 $\Omega$ , unless noted)

## $\label{eq:clc425} CLC425 \ Typical \ Performance \ (T_A=25^{\circ}C, \ V_{cc}=\pm5V, R_g=26.1\Omega\,, \ R_f=499\Omega\,, \ R_L=100\Omega\,, \ unless \ noted)$

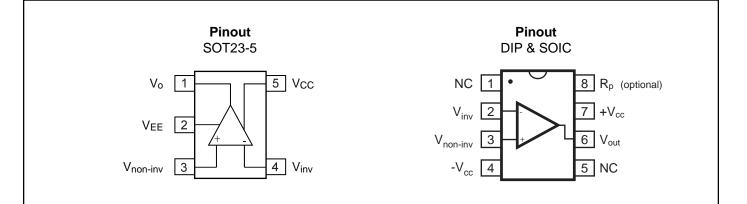

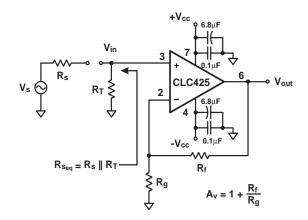

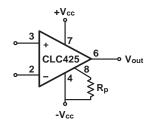

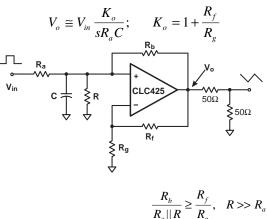

Figure 1: Non-inverting Amplifier Configuration

#### Introduction

The CLC425 is a very wide gain-bandwidth, ultra-low noise voltage feedback operational amplifier which enables application areas such as medical diagnostic ultrasound, magnetic tape & disk storage and fiber-optics to achieve maximum high-frequency signal-to-noise ratios. The set of characteristic plots located in the "Typical Performance" section illustrates many of the performance trade-offs. The following discussion will enable the proper selection of external components in order to achieve optimum device performance.

#### **Bias Current Cancellation**

In order to cancel the bias current errors of the noninverting configuration, the parallel combination of the gain-setting (R<sub>g</sub>) and feedback (R<sub>f</sub>) resistors should equal the equivalent source resistance (R<sub>seq</sub>) as defined in Figure 1. Combining this constraint with the non-inverting gain equation also seen in Figure 1, allows both R<sub>f</sub> and R<sub>g</sub> to be determined explicitly from the following equations: R<sub>f</sub>=A<sub>v</sub>R<sub>seq</sub> and R<sub>g</sub>=R<sub>f</sub>/(A<sub>v</sub>-1). When driven from a 0 $\Omega$  source, such as that from the output of an op amp, the non-inverting input of the CLC425 should be isolated with at least a 25 $\Omega$  series resistor.

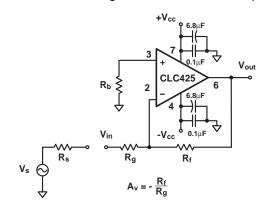

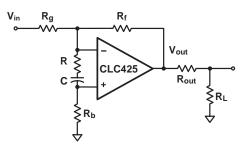

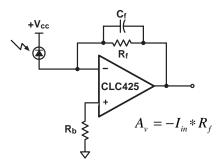

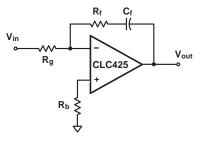

As seen in Figure 2, bias current cancellation is accomplished for the inverting configuration by placing a resistor ( $R_b$ ) on the non-inverting input equal in value to the resistance seen by the inverting input ( $R_f||(R_g+R_s))$ ).  $R_b$  is recommended to be no less than 25 $\Omega$  for best CLC425 performance. The additional noise contribution of  $R_b$  can be minimized through the use of a shunt capacitor.

Figure 2: Inverting Amplifier Configuration

#### **Total Input Noise vs. Source Resistance**

In order to determine maximum signal-to-noise ratios from the CLC425, an understanding of the interaction between the amplifier's intrinsic noise sources and the noise arising from its external resistors is necessary.

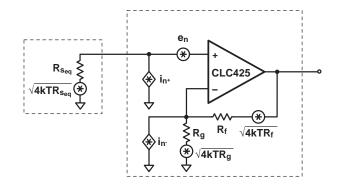

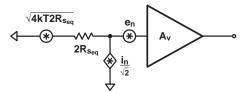

Figure 3 describes the noise model for the non-inverting amplifier configuration showing all noise sources. In addition to the intrinsic input voltage noise (e<sub>n</sub>) and current noise ( $i_n=i_{n+}=i_n$ ) sources, there also exists thermal voltage noise ( $e_t=\sqrt{4kTR}$ ) associated with each of the external resistors. Equation 1 provides the general form for total equivalent input voltage noise density ( $e_{ni}$ ). Equation 2 is a simplification of Equation 1 that assumes

#### Figure 3: Non-inverting Amplifer Noise Model

$$e_{ni} = \sqrt{e_n^2 + (i_{n+}R_{s_{eq}})^2 + 4kTR_{s_{eq}} + (i_{n-}(R_f ||R_g))^2 + 4kT(R_f ||R_g)}$$

#### **Equation 1: General Noise Equation**

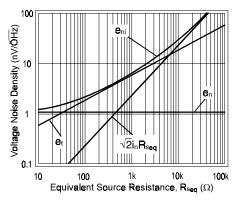

$R_{f}||R_{g} = R_{s_{eq}}$  for bias current cancellation. Figure 4 illustrates the equivalent noise model using this assumption. Figure 5 is a plot of  $e_{ni}$  against equivalent source resistance  $(R_{s_{eq}})$  with all of the contributing voltage noise sources of Equation 2 shown. This plot gives the expected  $e_{ni}$  for a given  $R_{s_{eq}}$  which assumes  $R_{f}||R_{g} = R_{s_{eq}}$  for bias current cancellation. The total equivalent output voltage noise  $(e_{no})$  is  $e_{ni}*A_{v}$ .

Figure 4: Noise Model with  $R_f ||R_g = R_{seq}$

$$e_{ni} = \sqrt{e_n^2 + 2(i_n R_{s_{eq}})^2 + 4kT(2R_{s_{eq}})^2}$$

Equation 2: Noise Equation with  $R_f ||R_g = R_{seq}$

As seen in Figure 5,  $e_{ni}$  is dominated by the intrinsic voltage noise  $(e_n)$  of the amplifier for equivalent source resistances below 33.5 $\Omega$ . Between 33.5 $\Omega$  and 6.43k $\Omega$ ,  $e_{ni}$  is dominated by the thermal noise  $(e_t=\sqrt{4kTR}_{seq})$  of the external resistors. Above 6.43k $\Omega$ ,  $e_{ni}$  is dominated by the amplifier's current noise  $(\sqrt{2i}_nR_{seq})$ . The point at which the CLC425's voltage noise and current noise contribute equally occurs for  $R_{seq}$ =464 $\Omega$  (i.e.  $e_n/\sqrt{2i}_n$ ). As an example, configured with a gain of +20V/V giving a -3dB of 90MHz and driven from an  $R_{seq}$ =25 $\Omega$ , the CLC425 produces a total equivalent input noise voltage  $(e_{ni}*\sqrt{1.57*90MHz})$  of 16.5 $\mu V_{rms}$ .

Figure 5: Voltage Noise Density vs. Source Resistance

If bias current cancellation is not a requirement, then  $R_f ||R_g$  does not need to equal  $R_{seq}$ . In this case, according to Equation 1,  $R_f ||R_g$  should be as low as possible in order to minimize noise. Results similar to Equation 1 are obtained for the inverting configuration of Figure 2 if  $R_{seq}$  is replaced by  $R_b$  and  $R_g$  is replaced by  $R_g+R_s$ . With these substitutions, Equation 1 will yield an  $e_{ni}$  referred to the non-inverting input. Refering  $e_{ni}$  to the inverting input is easily accomplished by multiplying  $e_{ni}$  by the ratio of non-inverting to inverting gains.

#### **Noise Figure**

Noise Figure (NF) is a measure of the noise degradation caused by an amplifier.

$$NF = 10LOG\left(\frac{S_i / N_i}{S_o / N_o}\right) = 10LOG\left(\frac{e_{ni}^2}{e_t^2}\right)$$

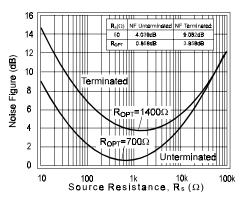

The Noise Figure formula is shown in Equation 3. The addition of a terminating resistor  $R_T$ , reduces the external thermal noise but increases the resulting NF. The NF is increased because  $R_T$  reduces the input signal amplitude thus reducing the input SNR.

$$NF = 10LOG\left(\frac{e_{n}^{2} + i_{n}^{2}\left(R_{seq} + \left(R_{f} / / R_{g}\right)^{2}\right) + 4kTR_{seq} + 4kT\left(R_{f} / / R_{g}\right)}{4kTR_{seq}}\right)$$

$R_{seq} = R_s$  for Unterminated Systems  $R_{seq} = R_s II R_T$  for Terminated Systems

- Minimize R<sub>f</sub>||R<sub>q</sub>

- Choose the optimum R<sub>s</sub> (R<sub>OPT</sub>)

R<sub>OPT</sub> is the point at which the NF curve reaches a minimum and is approximated by:

$$R_{OPT} \cong (e_n/i_n)$$

Figure 6 is a plot of NF vs  $R_s$  with  $R_f || R_g = 9.09$  ( $A_v = +10$ ). The NF curves for both Unterminated and Terminated systems are shown. The Terminated curve assumes  $R_s$ =  $R_T$ . The table indicates the NF for various source resistances including  $R_s = R_{OPT}$ .

Figure 6: Noise Figure vs Source Resistance

#### **Supply Current Adjustment**

The CLC425's supply current can be externally adjusted downward from its nominal value by adding an optional resistor ( $R_p$ ) between pin 8 and the negative supply as shown in Figure 7. Several of the plots found within the plot pages demonstrate the CLC425's behavior at different supply currents. The plot labeled " $I_{cc}$  vs.  $R_p$ " provides the means for selecting  $R_p$  and shows the result of standard IC process variation which is bounded by the 25°C curve.

Figure 7: External Supply Current Adjustment

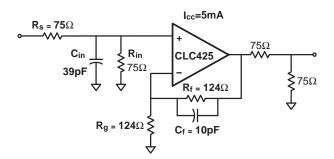

#### Non-Inverting Gains Less Than 10V/V

Using the CLC425 at lower non-inverting gains requires external compensation such as the shunt compensation as shown in Figure 8. The quiescent supply current must also be reduced to 5mA with  $R_p$  for stability. The compensation capacitors are chosen to reduce frequency response peaking to less than 1dB. The plot in the "Typical Performance" section labeled "Differential Gain and Phase" shows the video performance of the CLC425 with this compensation circuitry.

**Figure 8: External Shunt Compensation**

#### Inverting Gains Less Than 10V/V

The lag compensation of Figure 9 will achieve stability for lower gains. Placing the network between the two input terminals does not affect the closed-loop nor noise gain, but is best used for the invering configuration because of its affect on the non-inverting input impedance.

Figure 9: External Lag Compensation

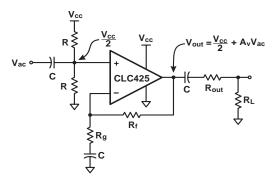

#### Single-Supply Operation

The CLC425 can be operated with single power supply as shown iin Figure 10. Both the input and output are capacitively coupled to set the dc operating point.

**Figure 10: Single Supply Operation**

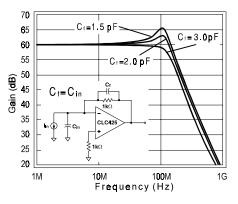

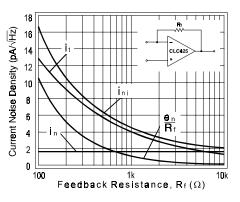

#### Low Noise Transimpedance Amplifier

The circuit of Figure 11 implements a low-noise transimpedance amplifier commonly used with photo-diodes. The transimpedance gain is set by R<sub>f</sub>. The simulated frequency response is shown in Figure 12 and shows the influence C<sub>f</sub> has over gain flatness. Equation 4 provides the total input current noise density (i<sub>ni</sub>) equation for the basic transimpedance configuration and is plotted against feedback resistance (R<sub>f</sub>) showing all contributing noise sources in Figure 13. This plot indicates the expected total equivalent input current noise density (i<sub>ni</sub>) for a given feedback resistance (R<sub>f</sub>). The total equivalent output voltage noise density (e<sub>no</sub>) is i<sub>ni</sub>\*R<sub>f</sub>.

Figure 11: Transimpedance Amplifier Configuration

Figure 12: Transimpedance Amplifier Frequency Response

Figure 13: Current Noise Density vs. Feedback Resistance

$$i_{ni} = \sqrt{i_n^2 + \left(\frac{e_n}{R_f}\right)^2 + \frac{4kT}{R_f}}$$

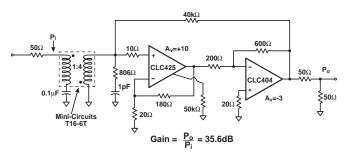

#### Very Low Noise Figure Amplifier

The circuit of Figure 14 implements a very low Noise Figure amplifier using a step-up transformer combined with a CLC425 and a CLC404. The circuit is configured with a gain of 35.6dB. The circuit achieves measured Noise Figures of less than 2.5dB in the 10-40MHz region. 3<sup>rd</sup> order intercepts exceed +30dBm for frequencies less than 40MHz and gain flatness of 0.5dB is measured in the 1-50MHz pass bands. Application Note OA-14 provides greater detail on these low Noise Figure techniques.

Figure 14: Very Low Noise Figure Amplifier

#### Low Noise Integrator

The CLC425 implements a deBoo integrator shown in Figure 15. Integration linearity is maintained through positive feedback. The CLC425's low input offset voltage and matched inputs allowing bias current cancellation provide for very precise integration. Stability is maintained through the constraint on the circuit elements.

Figure 15: Low Noise Integrator

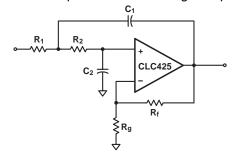

#### **High-Gain Sallen-Key Active Filters**

The CLC425 is well suited for high-gain Sallen-Key type of active filters. Figure 16 shows the 2<sup>nd</sup> order Sallen-Key low pass filter topology. Using component predistortion methods as discussed in OA-21 enables the proper selection of components for these high-frequency filters.

Figure 16: Sallen-Key Active Filter Topology

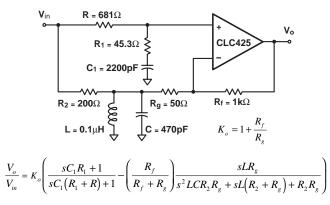

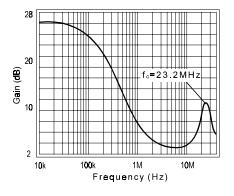

#### Low Noise Magnetic Media Equalizer

The CLC425 implements a high-performance low-noise equalizer for such applications as magnetic tape channels as shown in Figure 17. The circuit combines an integrator with a bandpass filter to produce the lownoise equalization. The circuit's simulated frequency response is illustrated in Figure 18.

Figure 17: Low Noise Magnetic Media Equalizer

Figure 18: Equalizer Frequency Response

#### Low-Noise Phase-Locked Loop Filter

The CLC425 is extremely useful as a Phase-Locked Loop filter in such applications as frequency synthesizers and data synchronizers. The circuit of Figure 19 implements one possible PLL filter with the CLC425.

Figure 19: Phased-Locked Loop Filter

#### **Decreasing the Input Noise Voltage**

The input noise voltage of the CLC425 can be reduced from its already low 1.05nV/ $\sqrt{Hz}$  by slightly increasing the supply current. Using a 50k $\Omega$  resistor to ground on pin 8, as shown in the circuit of Figure 14, will increase the quiescent current to  $\approx$ 17mA and reduce the input noise voltage to < 0.95nV/ $\sqrt{Hz}$ .

#### **Printed Circuit Board Layout**

Generally, a good high-frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillation, see OA-15 for more information. National suggests the CLC730013-DIP, CLC730027-SOIC, or CLC730068-SOT evaluation board as a guide for high-frequency layout and as an aid in device testing and characterization.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-532 93 58 National Semiconductor Hong Kong Ltd. 2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.